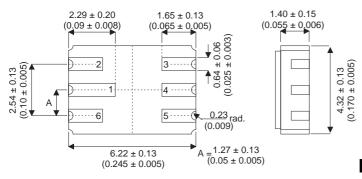

## **MECHANICAL DATA**

Dimensions in mm (inches)

## **CERAMIC LCC2 PACKAGE**

(Underside View)

| PAD 1 – DRAIN 1 | PAD 4 – DRAIN 2  |

|-----------------|------------------|

| PAD 2 – GATE 1  | PAD 5 – SOURCE 2 |

| PAD 3 – GATE 2  | PAD 6 – SOURCE 1 |

## DUAL N-CHANNEL ENHANCEMENT MODE MOSFET V<sub>DSS</sub> 90V

| I <sub>D</sub>      | 0.9 |

|---------------------|-----|

| R <sub>DS(on)</sub> | 4.0 |

#### **FEATURES**

- Faster switching

- Low Ciss

- Integral Source-Drain Diode

- High Input Impedance and High Gain

## DESCRIPTION

These Dual enhancement-mode (normally-off) vertical DMOS FETs are ideally suited to a wide range of switching and amplifying applications where high breakdown voltage, high input impedance, low input capacitance, and fast switching speeds are desired.

High Reliability Screening options are available.

## **ABSOLUTE MAXIMUM RATINGS** Each Side - T<sub>CASE</sub> = 25<sup>°</sup>C unless otherwise stated

| V <sub>DS</sub>     | Drain - Source Voltage                                |                                      | 90V          |

|---------------------|-------------------------------------------------------|--------------------------------------|--------------|

| I <sub>D</sub>      | Drain Current                                         | - Continuous ( $T_c = 25^{\circ}C$ ) | 0.9A         |

|                     |                                                       | - Continuous (T <sub>c</sub> = 100℃) | 0.7A         |

| I <sub>DM</sub>     | Drain Current                                         | - Pulsed (Note 1)                    | 3A           |

| $V_{GS}$            | Gate - Source Voltage                                 |                                      | ±20V         |

| P <sub>tot(1)</sub> | Total Power Dissipation at $T_{mb} \le 25$ °C         |                                      | 6.25W        |

|                     | De-rate Linearly above 25°C                           |                                      | 0.050W/℃     |

| P <sub>tot(2)</sub> | Total Power Dissipation at $T_{amb} \leq 25^{\circ}C$ |                                      | 0.5W         |

| $T_{j}, T_{stg}$    | Operating and Storage Junction Temperature Range      |                                      | -55 to +150℃ |

## THERMAL DATA

| R <sub>thj-mb</sub>                                                               | Thermal Resistance Junction – Mounting base  | Max | 20  | °C/W |  |

|-----------------------------------------------------------------------------------|----------------------------------------------|-----|-----|------|--|

| R <sub>thj-amb</sub>                                                              | mb Thermal Resistance Junction - Ambient Max |     | 250 | °C/W |  |

| NOTES: 1) Repetitive Rating: Pulse Width limited by maximum junction temperature. |                                              |     |     |      |  |

2) Starting  $T_J = 25^{\circ}C$ , L = 1.46mH, I<sub>AS</sub> = 48A, V<sub>DD</sub> = 50V, R<sub>G</sub> = 25 $\Omega$ ,

3) Pulse Test: Pulse Width ≤ 380µS, Duty Cycle , δ 2%

Semelab Plc reserves the right to change test conditions, parameter limits and package dimensions without notice. Information furnished by Semelab is believed to be both accurate and reliable at the time of going to press. However Semelab assumes no responsibility for any errors or omissions discovered in its use. Semelab encourages customers to verify that datasheets are current before placing orders.

**Semelab plc.** Telephone +44(0)1455 556565. Fax +44(0)1455 552612. E-mail: <u>sales@semelab.co.uk</u> Website: <u>http://www.semelab.co.uk</u>

# 2N6661DCSM

## 2N6661DCSM

#### Parameter **Test Conditions** Min. Тур. Max. Unit $V_{GS} = 0V$ Drain - Source Breakdown Voltage $I_{D} = 1.0 \mu A$ V<sub>(BR)DSS</sub> 90 - $V_{DS} = V_{GS}$ $I_D = 1.0 \text{mA}$ 0.8 2 V Gate - Source threshold Voltage T<sub>C</sub> = 125℃ V<sub>GS(th)</sub> 0.3 --T<sub>C</sub> = -55℃ 2.5 -- $V_{GS} = \pm 20V$ $V_{DS} = 0V$ --±100 Gate - Source Leakage Current nA I<sub>GSS</sub> T<sub>C</sub> = 125℃ ±500 -- $V_{DS} = 72V$ $V_{GS} = 0V$ 1.0 --Zero Gate Voltage Drain Current IDSS μΑ T<sub>C</sub> = 125℃ 100 -- $V_{DS} = 15V$ $V_{GS} = 10V$ \_ А On – State Drain Current (note 3) 1.5 I<sub>D(on)</sub> - $V_{GS} = 5V$ $I_{D} = 0.3A$ 5.3 --Drain – Source On Resistance R<sub>DS(on)</sub> $V_{GS} = 10V$ $I_{D} = 1.0A$ 4 Ω --(note 3) T<sub>C</sub> = 125℃ 7.5 -- $V_{GS} = 5V$ $I_{D} = 0.3A$ 1.6 -- $V_{GS} = 10V$ $I_{D} = 1.0A$ V<sub>DS(on)</sub> Drain – Source On Voltage (note 3) --4 V T<sub>C</sub> = 125℃ 7.5 --Forward Transconductance (Note 3) $V_{DS} = 7.5V$ $I_{D} = 0.475A$ 170 \_ ms **g**<sub>FS</sub> V $V_{SD}$ Diode Forward Voltage (Note 3) $V_{GS} = 0V$ $I_{s} = 0.86A$ 0.7 1.4 \_

## STATIC ELECTRICAL RATINGS (Each Side - T<sub>case</sub>=25°C unless otherwise stated)

## DYNAMIC CHARACTERISTICS

| C <sub>iss</sub>    | Input Capacitance            | $V_{DS} = 25V$<br>f = 1.0MHz $V_{GS} = 0V$ |                     | -  | 50 | -  |    |

|---------------------|------------------------------|--------------------------------------------|---------------------|----|----|----|----|

| C <sub>oss</sub>    | Output Capacitance           |                                            | -                   | 40 | -  | pF |    |

| C <sub>rss</sub>    | Reverse Transfer Capacitance |                                            |                     | -  | 10 | -  |    |

| T <sub>d(on)</sub>  | Turn-On Delay                | $V_{DD} = 25V$                             | I <sub>D</sub> = 1A | -  | 10 | -  |    |

| T <sub>d(off)</sub> | Turn-Off Delay Time          | $R_{GS} = 50\Omega$                        | (Note 3)            | -  | 10 | -  | ns |

### MATCHING CHARACTERISTICS FET1 to FET2

| V <sub>GS(th) M</sub> | Gate – Source threshold Voltage<br>Matching | $V_{DS} = V_{GS}$ | I <sub>D</sub> = 1mA    | - | - | ±25 | mV |

|-----------------------|---------------------------------------------|-------------------|-------------------------|---|---|-----|----|

| <b>g</b> fsm          | Forward Transconductance Matching (Note 3)  | $V_{DS} = 7.5V$   | I <sub>D</sub> = 0.475A | - | - | 50  | ms |

Semelab Plc reserves the right to change test conditions, parameter limits and package dimensions without notice. Information furnished by Semelab is believed to be both accurate and reliable at the time of going to press. However Semelab assumes no responsibility for any errors or omissions discovered in its use. Semelab encourages customers to verify that datasheets are current before placing orders.

**Semelab plc.** Telephone +44(0)1455 556565. Fax +44(0)1455 552612. E-mail: <u>sales@semelab.co.uk</u> Website: <u>http://www.semelab.co.uk</u>